半導体試験装置(テスタ)

Testalio / テスタリオ

ウェーハ検査工程やパッケージ後の最終工程でデバイスの良否判定をおこなう装置です。

製品名のTestalioは「Tester+All in one」を意味し、ユーザーニーズに合わせたオールインワン型の4つのモデル展開でテスト環境を最適化します。

テスト環境や予算に応じ、ご要望に合わせて機能を絞り込んだコストパフォーマンスの高い専用テスタ/テストシステム開発を承ります

-

01要望に応じた新たなテスト・モジュールの提供が可能で、幅広いデバイスのテスト最適化に対応

-

02テストパターンの容量制限がなく、大規模なデバイスのテストも可能

-

03テスト・モジュール構成に応じ筐体サイズを4タイプより選択可能

-

04筐体内に電源・制御PCを内蔵し省スペース

お客さまのデバイスやテスト環境に対応した4種類の共通プラットフォーム筐体を用意し、必要なチャネル数に応じて幅広いアプリケーションモジュールを提供

使用環境ごとの推奨機種

・設計検証/不良解析

CT-025 / CT-050

・量産

CT-050 / CT-100 / CT-200

半導体試験装置(テスタ)とは

半導体テスタとは、半導体デバイスに電気信号などを与え、出力される信号を期待値と比較することで、設計仕様通りに動作するかどうかを検査する装置です。ATE(Automated Test Equipment)ともよばれています。

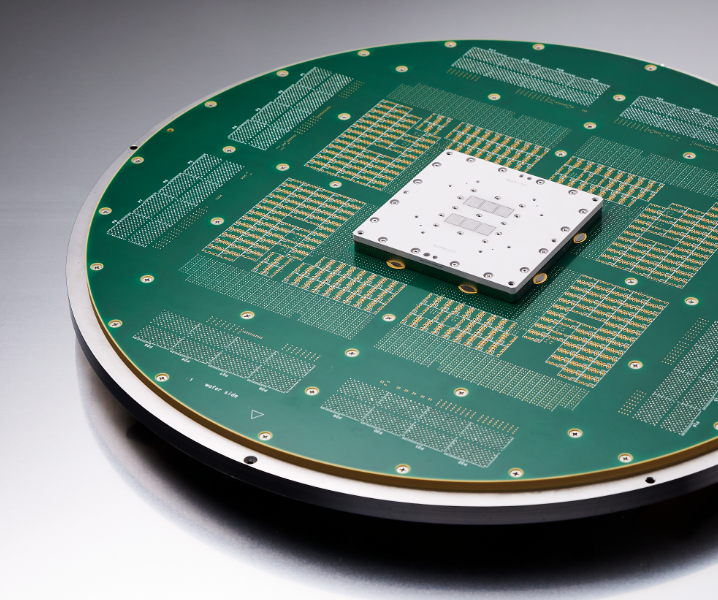

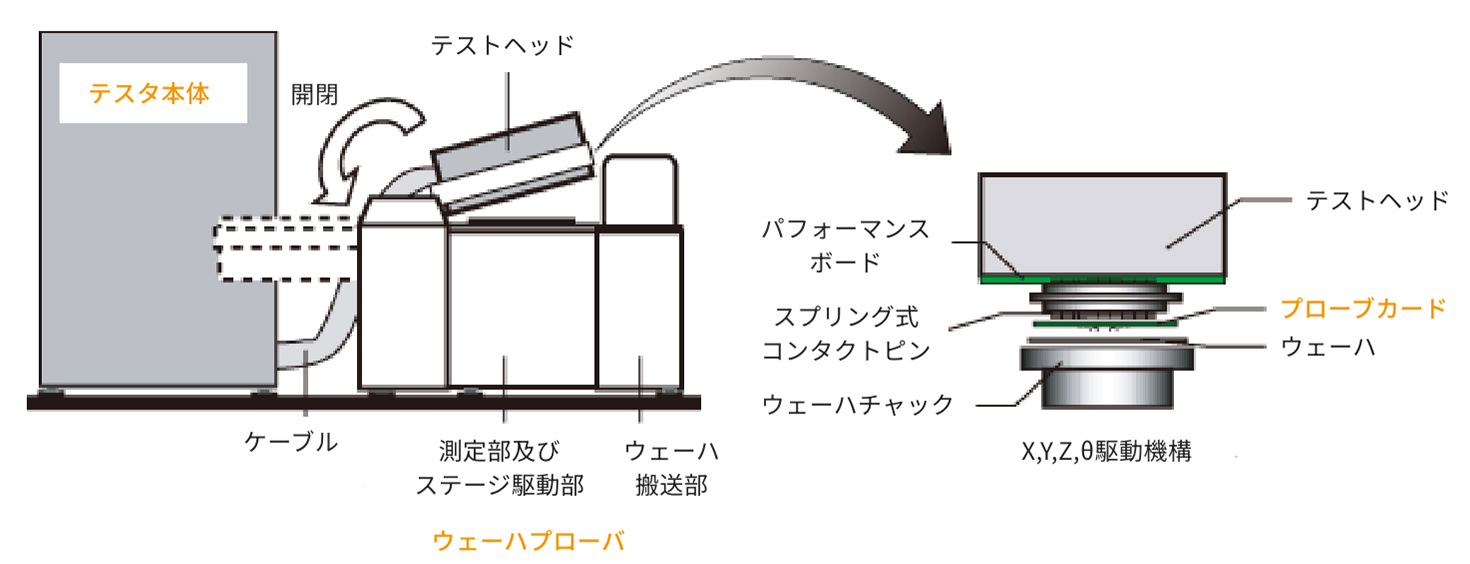

テスタはロジックテスタ、メモリテスタ、アナログテスタに大きく分類されます。通常半導体の検査は、ウェーハ状態で検査するウェーハ検査(ダイ・ソートやプローブ検査などとも呼ばれる)と、パッケージ後に行なわれるパッケージ検査(ファイナル検査などとも呼ばれる)の2段階で行なわれます。ウェーハ検査ではプローバとプローブカードが、パッケージ検査ではハンドラーとテストソケットが、それぞれテスタと共に用いられます。

【テスタ】

【ウェーハ検査装置】

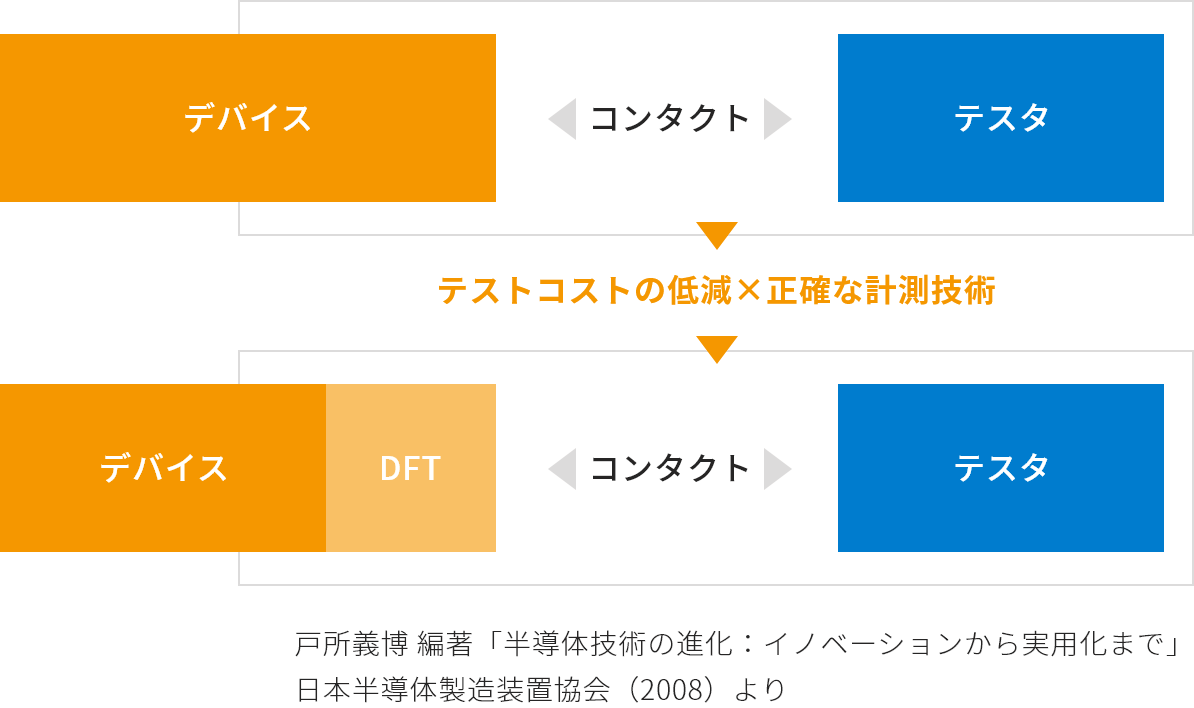

DFTとは

DFT (Design For Testability) はテスト容易化設計のことです。

IC 設計の初期段階から、テストのし易さを考慮した回路の構造にしたり、テスト用回路の組込みなどを行います。正確なテストを短時間に行え、テストコストの低減が期待できます。BIST や Scan テストが DFT の代表的な例として挙げられます。

BISTとは

BIST(Built-in Self Test)はDFT技術の1つです。

本来テスタが持つ機能の一部を、ICの回路の内部に組み込んで、IC自身が自己テストを行う手法です。IC内のBIST回路にはテスト対象回路に加えるテスト・パターン生成、テスト対象からの出力パターン圧縮、圧縮されたパターンと期待値との比較、などの機能が含まれます。テスタに要求される機能が限定される、同時に多数のICの検査が行えるなど、テストコストの低減も期待できます。メモリ回路検査用のメモリBIST、ロジック回路検査用のロジックBISTなどがあります。

SCANテストとは

ScanテストもDFT技術の1つで、ロジック回路をテストする手法の1つです。

構造検査のひとつで、IC内部の回路のオープンやショートなどにより論理値が常に1もしくは0になるモードの故障を検出します。

Scanテスト時にIC内部にテスト用のScanチェーンと呼ばれるFF(フリップフロップ)のチェーンを構成します。テスタからのテストパタンデータをFFのチェーン経由でテスト対象回路ブロックに送り、テスト対象の内部状態を反映した応答をFFのチェーン経由で取り出します。予め想定した応答パターンと比較する事で内部の故障個所が検出できます。

故障モデルを予め想定し、回路設計データから不良を特定しやすくするパターンをソフトウェアによって自動で生成する事で、大規模なICでも短時間で故障検出率の高いテストが行えます。